Research

This page gives a quick tour through my main research interests and activities since 2003. These involved computer architecture and arithmetic, but also high-level methodologies and formal/theoretical approaches for automatically designing and building architectures with given properties. In a nutshell, my research covers:

- Computer arithmetic and architectures for cryptography-related operations

- architectures for modular arithmetic, GF(2m) operations, and unified arithmetic in GF(p) and GF(2m)

- speculative addition and multiplication

- exploitation of emerging computational models such as Threshold Logic

- Complex on-chip systems and architectures for heterogeneous HPC

- parallel programming paradigms for electronic system-level design

- automated OpenMP-to-hardware translation (syMParallel toolchain)

- exploration of customized and GPU-like architectures for HPC (take a look at the NaplesPU website)

- memory optimization in High-Level Synthesis (HLS) toolflows

- automated synthesis of complex on-chip interconnects

- exploration of innovative models and architectures for optical and hybrid on-chip interconnects

- industrial applications of FPGAs in mission-critical applications

- Applied research in the domain of security-critical and embedded applications

- secure distribution of FPGA-based hardware cores

- infrastructures for digital time stamping

- security algorithms and protocols for resource constrained and embedded systems

- SmartCard-based innovative applications

Jump to this section below for my Editorial and review activities, or the Publications page, Projects page, and Acknowledgements page for the respective detailed contents. Otherwise, you might read through the lengthy descriptions of my research activities given below.

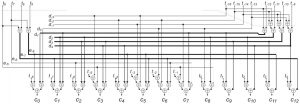

An SPB GF(2m) multiplier (from Cilardo, IEEE Trans. Comp., 2009)

At the lowest level, my activities involved devising advanced hardware blocks for particularly challenging operations, like those used in cryptography, most notably operations in algebraic structures known as binary finite fields, or GF(2m), as well as modular integer arithmetic, used in widespread cryptographic algorithms like RSA and Elliptic Curve cryptography. While focused on implementation aspects, this line of research allowed a deeper understanding of the mathematical basic building blocks in GF(2m) and integer modular arithmetic, leading to novel unified approaches for those two classes of operations, new parallel GF(2m) multiplier architectures, and even the exploitation of emerging computational models such as Threshold Logic. These results are described in a number of works, including several IEEE Transactions on Computers papers.

The FPGA in the Cloud poster

As a more practical development, I also designed and supervised the development of an FPGA-based accelerator for Homomorphic Encryption targeting server/cloud environments, which received the ALTERA Innovate Europe award. Along this line, my work also focused on low-level arithmetic operations, particularly integer addition on long operands, recurrent in cryptographic applications. One of the approach I explored relied on new speculative schemes, allowing shorter combinatorial propagation delays and hence faster circuits, although these circuits might occasionally generate wrong results that need to be corrected. I also evaluated dedicated acceleration solutions for cryptanalytic applications, where your compute power is essentially aimed at breaking cryptographic algorithms to demonstrate possible weaknesses. Relying on a cluster of IBM CellBE processors (made available by the Barcelona Supercomputing Center) and, later, on a cluster of FPGAs, I was able to identify, respectively, an actual collision for a 71- and 72-round version of SHA-1, the first ever at the time of the respective works.

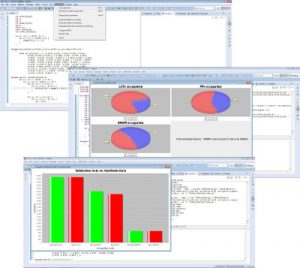

A few results from syMParallel

At a higher level, and more recently in my course of research, the focus moved to general digital design automation for complex on-chip systems and architectures for chip-level communication infrastructures. While a few results have implications for ASIC design, most of the ideas explored targeted FPGAs, which provide the unparalleled opportunity of customizing the system architecture driven by the application requirements. I thus explored parallel programming paradigms for electronic system-level design, which might potentially give a role to FPGAs in real heterogeneous computing settings. Concretely, this involved the automated generation of on-chip multiprocessor systems from high-level code (particularly, see the OpenMP-based syMParallel toolchain). The on-chip memory and interconnection infrastructure offers potential benefits for application-driven customization. I thus investigated memory optimization in High-Level Synthesis (HLS) toolflows, based on polyhedral compilation techniques to support the high-level code analysis and lattice-based partitioning to model the data layout in multi-bank memory. In addition, the on-chip interconnection infrastructure, and possibly its application-driven customization, are essential to performance, so my work also addressed the automated synthesis of complex on-chip interconnects, particularly heterogeneous architectures made of hierarchical buses and crossbars.

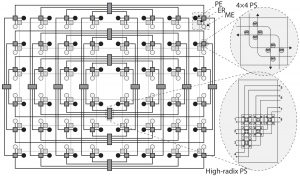

A picture from my IEEE TVLSI 2016 paper

Some of the results achieved along this line were also applied to underlying physical technologies different than standard Silicon processes, by exploring innovative models and architectures for optical and hybrid on-chip interconnects. While those works didn’t (of course) deal with the underlying physics, emerging on-chip optical technologies expose inherently different features and requirements, affecting the logical architectures being built on top of them.

The NaplesPU datapath

Most of the above activities revolved around architectural exploration. This is the key insight behind one project where I have a key role as a core team member, MANGO (H2020-FETHPC-2014 “MANGO: exploring Manycore Architectures for Next-GeneratiOn HPC systems”, ID 671668). Among other developments, one central activity planned and led by me is the development of a customizable manycore system based on GPU-like core, acting both as a tool for architectural exploration in ASIC development and as a deeply customizable FPGA overlay to be used to let reconfigurable hardware platforms exploit application-driven customization while still being programmable in pure software (a key prerequisite to ensure the actual usability of heterogeneous platforms in real environments). In fact, the GPU-like core, dubbed Naples Processing Unit, or NaplesPU (previously codenamed nu+ in MANGO), also comes with a full compilation toolchain, based on LLVM, which will ultimately also feature application-driven customization knobs. My aim is to demonstrate the impact of the GPU-like concept in fields like scientific and parallel computing by porting demanding data-parallel applications and co-optimizing the NaplesPU hardware/software infrastructure in a deeply application-driven way. A research proposal based on NaplesPU was recently granted the Intel Hardware Acceleration Research Program (HARP) v2, offering early access to the new CPU+FPGA (Broadwell + Arria10) MCP solutions provided by Intel to selected research centers worldwide. (Take a look at the NaplesPU website)

As more specific developments, my research activity also focused on industrial applications of FPGAs in mission-critical contexts as well as new implications of hardware reconfigurability for testing, particularly techniques for online testing as well as application-dependent testing (ADT).

Because of the central focus of security applications, my research activity did not only focus on low-level compute technologies. In fact, at even a higher level, a further branch of the activity covered security applications, particularly in embedded/mobile systems. Early works covered the implementation, deployment, and evaluation of security services in distributed environments, with special focus on time-stamping and public-key certification services. A line of works addressed SmartCard-based innovative applications based on technologies like Near-Field Communication and SCWS, in their infancy at the time (see also the Acknowledgements page for further details). A more recent development involves the interplay between security services and hardware reconfigurability in contexts where hardware cores can be distributed –pretty much like software digital contents– to FPGA mobile or in-field devices.

I’ve also been cooperating with industry and I’ve been involved in a number of projects and contracts with several companies, including the Italian Aerospace Research Centre (CIRA), MBDA, Ansaldo STS, STMicroelectronics, and others, serving as the coordinator for most of them. Past activities were mostly centered on the design of data processing hardware components and embedded systems, mostly based on FPGA technologies, with critical requirements in terms of performance, reliability, and/or security.

I’ve been working for funding agencies as an expert/reviewer, particularly for the Executive Agency for Higher Education, Research, Development and Innovation Funding (UEFISCDI) since 2011, and the Ministero dell’Istruzione, dell’Università e della Ricerca (MIUR) as a Reviewer/Rapporteur for the Progetti di Ricerca di Interesse Nazionale (PRIN) programme as well as the Futuro in Ricerca programme and the Scientific Independence of young Researchers (SIR) programme.

A couple of words about scientific production. Many of the above activities are described in my publications (listed here) and are linked with past/ongoing research projects. In my course of research I’ve been avoiding low-quality venues and predatory journals (at least, I tried to do so most of the time) and I’m not really keen on massive scientific production. For my main works I targeted reputable and highly selective journals, including several IEEE and ACM transactions and other high-rank journals, as well as recognized conferences and international events such as DATE, FPL, ITC, etc..

Sadly enough, my research areas are a sort of niche “market” in computer science. So, if you’re a fan of bibliometrics, don’t expect astronomic numbers in my Scholar profile (indeed, if you really are a fan of bibliometrics, you’re probably not that kind of person who likes reading through actual contents in a paper.. so you probaby didn’t even reach this point in the page). Also, I distrust suspiciously long author lists in scientific papers –a bibliometric free lunch– and I’m proudly the single author for a number of works (and main author of most of the remaining). Sarcastically, I might say that yes, I’m proudly the author of my papers.

Memberships and Editorial activities

I’m a Senior Member of the IEEE, a member of the IEEE Industrial Society, and a member the HiPEAC network.

I’m an Associate Editor of IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I), the flagship journal of the IEEE Circuits and Systems Society. My specific EDICS fields of interest include: Computer aided design and synthesis, Behavioural and multi-domain simulation, Arithmetic circuits and systems, Digital circuits and systems for cryptography, Low power digital systems, Reconfigurable and field programmable digital circuits, Digital VLSI, Digital hardware for signal processing.

I’m an Associate Editor of IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I), the flagship journal of the IEEE Circuits and Systems Society. My specific EDICS fields of interest include: Computer aided design and synthesis, Behavioural and multi-domain simulation, Arithmetic circuits and systems, Digital circuits and systems for cryptography, Low power digital systems, Reconfigurable and field programmable digital circuits, Digital VLSI, Digital hardware for signal processing.

I’ve also served as an Associate Editor of IEEE Transactions on Circuits and Systems II: Express Briefs (TCAS-II) which –incidentally– is independently managed, that is, there’s no connection between my roles as AE for the two journals. The EDICS fields are essentially the same as they are all centered around digital technologies.

I’ve also served as an Associate Editor of IEEE Transactions on Circuits and Systems II: Express Briefs (TCAS-II) which –incidentally– is independently managed, that is, there’s no connection between my roles as AE for the two journals. The EDICS fields are essentially the same as they are all centered around digital technologies.

I’m part of the Editorial Board of Elsevier Microprocessors and Microsystems: Embedded Hardware Design (MICPRO), covering embedded system hardware platforms, multi-processor systems on a chip (MPSoCs), programmable/reconfigurable hardware platforms, memory subsystems, communication infrastructures and networks-on-chip (NoCs), design methodologies, techniques, and tool flows as well as hardware/software co-design.

I’m part of the Editorial Board of Elsevier Microprocessors and Microsystems: Embedded Hardware Design (MICPRO), covering embedded system hardware platforms, multi-processor systems on a chip (MPSoCs), programmable/reconfigurable hardware platforms, memory subsystems, communication infrastructures and networks-on-chip (NoCs), design methodologies, techniques, and tool flows as well as hardware/software co-design.

I’ve also been an Associate Editor of Wiley/Hindawi  Security and Communication Networks, publishing original papers and review articles on all security areas including network security, cryptography, cyber security, etc. with emphasis on security protocols, approaches, and techniques applied to information processing systems and communication networks.

Security and Communication Networks, publishing original papers and review articles on all security areas including network security, cryptography, cyber security, etc. with emphasis on security protocols, approaches, and techniques applied to information processing systems and communication networks.

Please consider submitting works dealing with the above topics. Should you submit a paper on my fields of interest, there are some chances that I’ll be in charge of handling your manuscript!

Since 2003, I’ve been participating in the activities of international conferences and workshops as a speaker, session chair, secondary reviewer, technical program committee member, invited speaker, panelist, and track chair. The most important venues include DATE conference (11 accepted papers presented as of 2016), FPL, HPCC, DSD, VLSI-SoC, ICESS, 3PGCIC, ITC, and PDP.

I’ve been serving as a reviewer for countless scientific journals and conferences, including many IEEE and ACM transactions. My reviews often happen to be lengthy and meticulous. Trivial enough, I’m strongly convinced that a good peer-review-based system inherently depends on good reviews. This sounds obvious, but often doesn’t happen to be the case.

Recent Comments